Dual In-Line Memory Modules

What is DIMM?

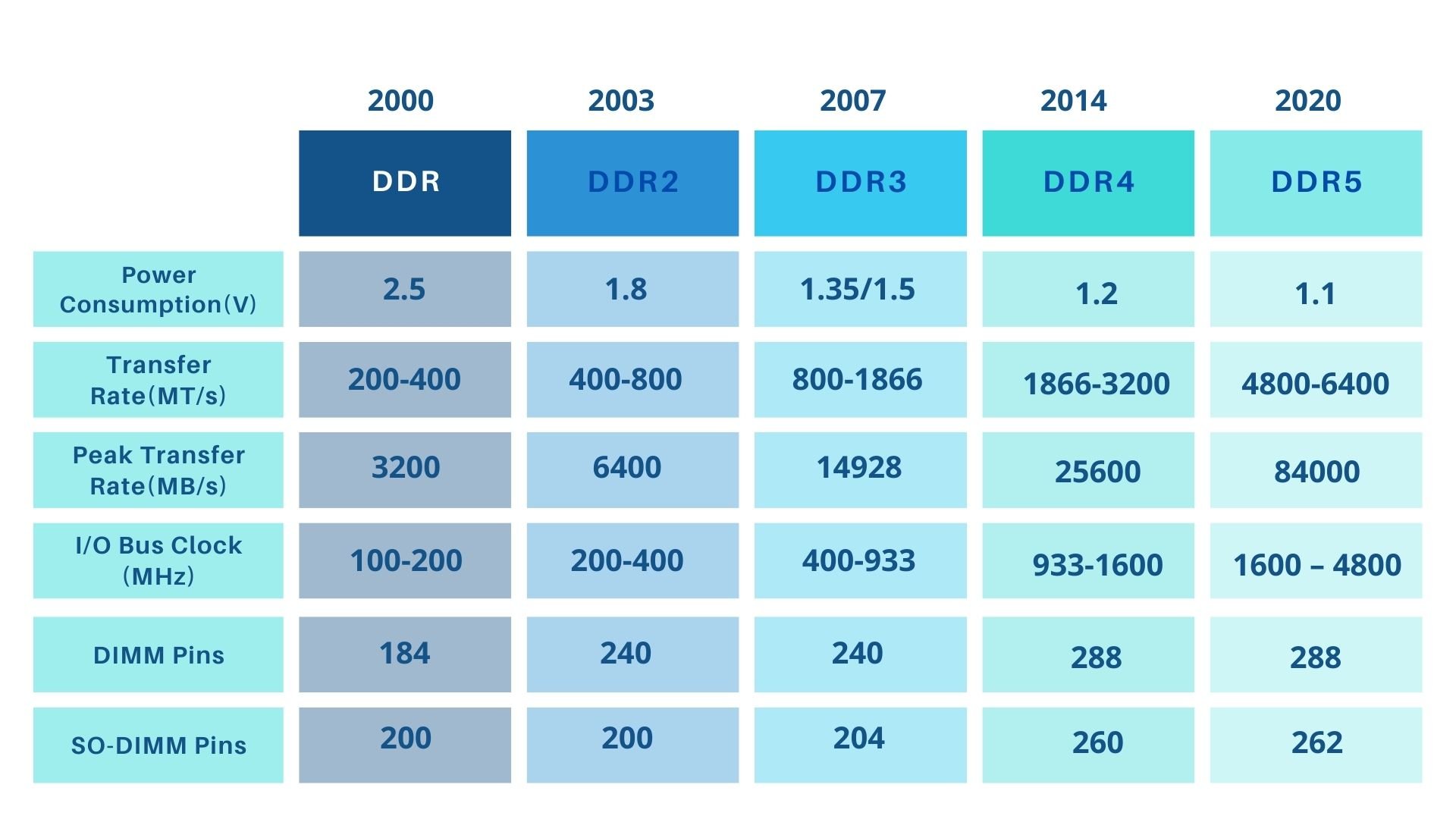

DIMM stands for Dual Inline Memory Module. DIMM is a module containing one or several Random Access Memory (RAM) or Dynamic RAM (DRAM) chips on a long, thin strip of printed circuit board with pins that connect it directly to the computer motherboard. A DIMM (of DDR2 or DDR3 sockets) typically has a 240-pin connector and supports 64/72-bit data transfer. Modern DIMMs based on double data rate fourth-generation (DDR4) or the latest double data rate fifth-generation (DDR5) use 288-pin connectors to computer motherboards, improving data throughput.

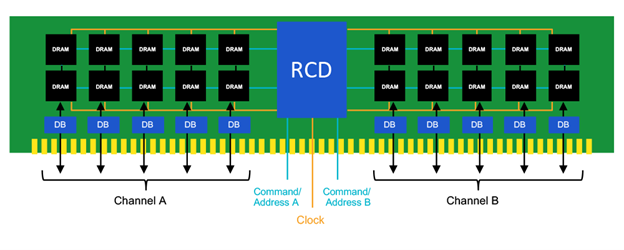

Dual Inline refers to pins on either side of the module. Chips on the DIMM are arranged in groups called ranks that can be accessed simultaneously by a memory controller. Within a single memory cycle, 64 bits of data can be accessed. Depending on how the DIMM is organized, these 64 bits may come from either the 8 or 16 DRAM chips. The number of ranks on any DIMM indicates the number of independent sets of DRAMs that can be accessed for a complete data bit-width of the DIMM (i.e., 64 bits).

Exemplary DDR5 DIMM Chipset from Rambus with registering clock drivers (RCD) and data buffers (DB) (Ref: rambus.com)

Comparison of different DDR generations (Ref: atpinc.com)

Today, DIMM has become the predominant memory module on the market because it is natively 64 bits, allowing faster data transfer than its 32-bit SIMM (single inline memory module) predecessor while consuming less power. Common types of DIMMs include UDIMMs (unbuffered DIMMs), FB-DIMMs (fully-buffered DIMMs), RDIMMs (registered DIMMs), LRDIMMs (load-reduced DIMMs), SO-DIMMs (small outline DIMMs), and ECC DIMMs (Error Correction Code).

Type of DIMM and primary applications

Generally, there are two significant classifications of DIMMs- registered and unregistered (or unbuffered). Unregistered DIMM (UDIMM) is mainly directed towards the consumer market, where the associated systems do not require supporting a considerable amount of memory. A UDIMM allows the memory controller to address each memory chip individually in a parallel fashion. Therefore, a limited number of memory chips can be used while maintaining stable and consistent performance. Typically, UDIMMs used in desktop computers support either x8 or x16 organization and up to 2 ranks per DIMM.

SO-DIMMs are preferred for systems with limited space, such as notebooks or laptops, as they are smaller than standard DIMM. For example, a small dual inline memory module (SO-DIMM) can be only 2.74 inches in size. The most common height for such DIMMs is 1.2 inches, but variations are also available in a shallow profile (VLP) form factor and are only 0.72 inches high.

FB-DIMMs (fully-buffered DIMMs) are mainly used as main memory in systems that require large capacities, such as servers and workstations. FB-DIMM uses Advanced Memory Buffer (AMB) chips to improve reliability, maintain signal integrity and boost error detection methods to reduce soft errors. The AMB bus is usually divided into a 14-bit read bus, and a 10-bit write bus. Each bit is carried over a differential pair, clocked at 12 times the introductory memory clock rate, six times the double-pumped data rate.

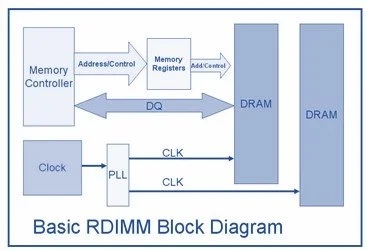

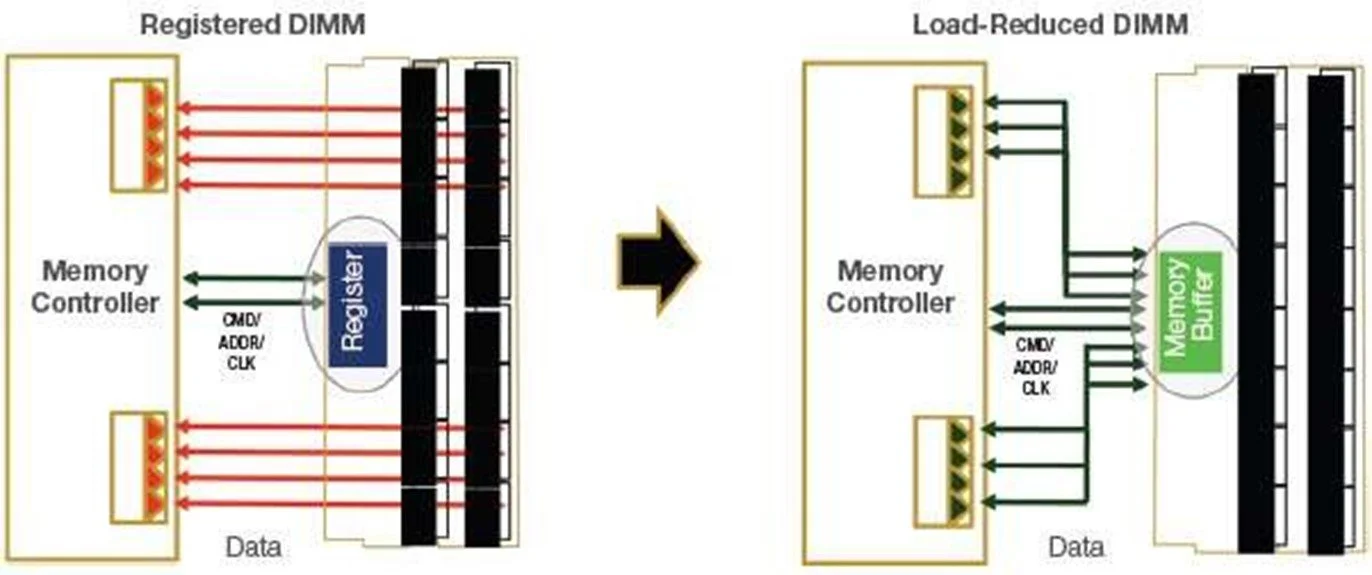

Servers running enterprise applications require a high density of the memory. However, with these high densities, the connection between the memory controller and the DRAM chips can often overload, causing errors and delays in data transfer. A register is placed between the DRAM chips and the memory controller to overcome this challenge, enhancing clock, command, and control signals. This additional register, also referenced as a buffer, isolates the control lines between each DRAM chip's memory controller. Accordingly, this reduces the electrical load, allowing the memory controller to address more DRAM chips while maintaining stability. Such registered DIMMs are commonly known as RDIMMs. Typically, RDIMMs used in server support are either x4 or x8 organization and up to 4 (but mostly 2) ranks per DIMM.

Basic RDIMM block diagram (Ref: simmtester.com)

As the name implies, Load-Reduced DIMMs (LRDIMMs) includes a memory buffer (similar to R-DIMMs) to reduce the load. LRDIMMs were introduced in the third generation of DDR memory (DDR3) and buffers both the control and data (DQ) lines from the DRAM chips. Unlike DDR3 Register Buffer (SSTE32882), which only buffers Command, Address, Control, and Clock, the LRDIMM Memory Buffer also buffers the Data (DQ) interface between the Memory Controller and the DRAM components. The Memory Buffer interface is responsible for memory requests to and from the local DIMM. LRDIMM provides a high memory bandwidth, large capacity channel solution for DDR3 central memory systems. This decreases the electrical load on the memory controller and allows for denser memory configurations—the increased memory capacity results in increased power consumption. However, implementing the buffer structure differently provides substantially higher operating data rates than RDIMMs of a similar configuration. Typically, LRDIMMs are used in server support x4 organization and up to 4 ranks per DIMM.

VLP SORDIMM SOUDIMM (Ref: Netlist)

RDIMM UDIMM (Ref: Netlist)

The increased capacity and performance of LRDIMMs come from the abstraction of DRAM chips and especially the rank count by the buffer. RDIMMs register buffers the command and address alone while leaving unbuffered the relatively more critical data bus. This leaves the group of DRAM chips exposed to the memory controller. In such a scenario, the memory controller simultaneously accesses the grouped DRAM chips.

By way of an example, a Quad-rank DDR3 RDIMM configuration presents four separate electrical loads on the data bus per RDIMM. The memory controller can handle up to a certain amount of load, and therefore, there is a limitation on the number of exposed ranks. To scale to high speeds, LRDIMMs use rank multiplication (for example, 2:1 or 4:1, up to a maximum of 8 physical ranks per LRDIMM), where multiple ranks appear to the memory controller as a logical rank of a larger size.

Comparison of system-level block diagrams for RDIMM vs. LRDIMM (Ref: edn.com)

ECC DIMMs come in both UDIMM and SODIMM configurations for server applications and can detect and correct data corruption, thereby reducing the number of crashes.

IP-Moats in DIMM

Intel, Ramaxel, Rambus, Micron, Samsung, Innodisk, and SK Hynix are the leading players in the global DIMM market. Interestingly, this market is semi-consolidated with only a few market players like Samsung, SK Hynix, etc., holding a majority of the market share. In contrast, several market players hold only a minor market share.

Lumenci recently discussed how a sophisticated IP-Moat acts as an anchor while the engineering and R&D teams adapt to the ever-changing tides of technology. For example, let’s review the IP-Moats of these leading players in the last ten years using the US patents granted on inventions related to LRDIMMs. The top ten assignees in the US with patents granted in this domain include Samsung, SK Hynix, Rambus, Intel, Inphi, IDT, IBM, Dell, Netlist, and Micron, as shown below.

Top Assignees with US Patent Grants on LR-DIMMs from 2012-2022 (Total grants: 524)

(Source: Lumenci)

From our analysis, it appears that the majority of the granted patents fall under either the G11C (devices or arrangements for storage of digital or analog information) or G06F (Electric Digital Data Processing) CPC codes followed by the USPTO. This indicates that the major players in this market obtain competitive edge from innovation arising from both the device design and the data handling of the LRDIMMs. Few of the old players like Samsung and SK Hynix are the leading patent owners that contribute to nearly two-thirds of the US patent grants. This trend correlates well with the proportion of their market share.

Future Outlook

With the voracious demands for greater memory bandwidth and capacity to support advanced workloads such as AI/ML and HPC, we can anticipate several new module architectures in the global DIMMs market in the next ten years. It would also be interesting to follow the IP strategy of big players such as Samsung and SK Hynix as they innovate to meet the new demands for greater memory bandwidth coming from emerging applications such as data centers, IoT networks, autonomous vehicles, etc.

*Disclaimer: This report is based on information that is publicly available and is considered to be reliable. However, Lumenci cannot be held responsible for the accuracy or reliability of this data.

*Disclaimer: This report is based on information that is publicly available and is considered to be reliable. However, Lumenci cannot be held responsible for the accuracy or reliability of this data.

Author

Editorial Team at Lumenci

Through Lumenci blogs and reports, we share important highlights from the latest technological advancements and provide an in-depth understanding of their Intellectual Property (IP). Our goal is to showcase the significance of IP in the ever-evolving world of technology.