RISC - Reduced Instruction Set Computer

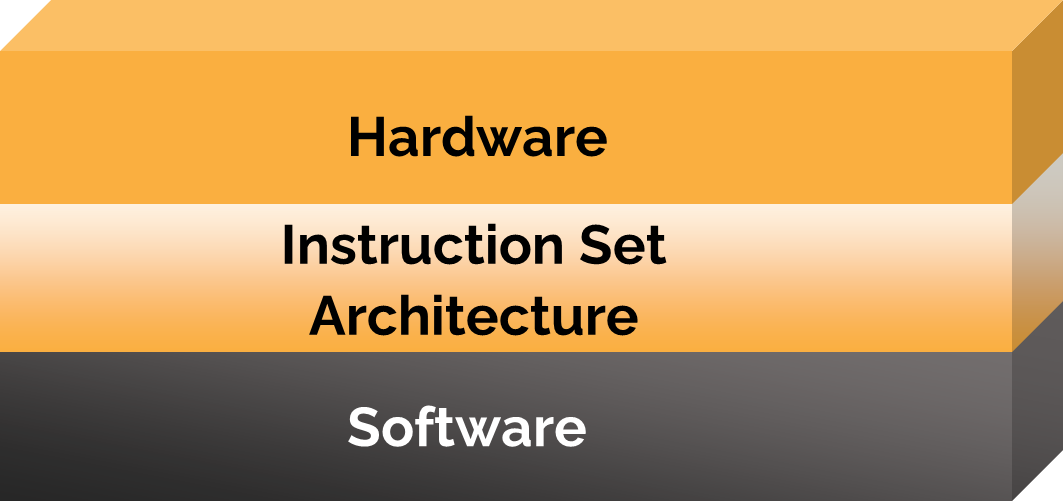

How people interact with each other and in which manner depends from person to person. Communication between human beings can be done in many ways, i.e., we can express our feelings by using hand gestures and/or different languages to coordinate with each other. But in the case of laptops, mobiles, gaming consoles, televisions, etc., the interaction between the software and the hardware is governed by Instruction Set Architecture (ISA).

An Instruction Set Architecture (ISA) acts as a medium between the hardware and software, which defines how the software controls the Central Processing Unit (CPU). ISA is a part of the processor and defines the capability of the processor to perform different tasks in different ways. It is visible to the application programmer, compiler writer, and assembly language programmer. ISA describes the registers, data types, supported instructions executed by the microprocessor, virtual memory management, hardware support for central memory management, addressing modes, and compiling the programs to the processor. An ISA can be extended by adding instructions or other capabilities or adding support for larger addresses and data values.

How ISA interacts between Hardware and Software (Source: Lumenci)

An ISA can be commonly classified in terms of architectural complexity, namely CISC and RISC. The Complex Instruction Set Computer (CISC) defines a microprocessor architecture in which a single instruction can execute a multi-step operation (like arithmetic operation, load/store memory, etc.) or addressing modes. As each instruction performs many operations, it takes several clock cycles to complete. These instructions having variable lengths result in increased processing time. Also, many transistors (in hardware space) used here for storing complex instructions result in increased power consumption and cost.

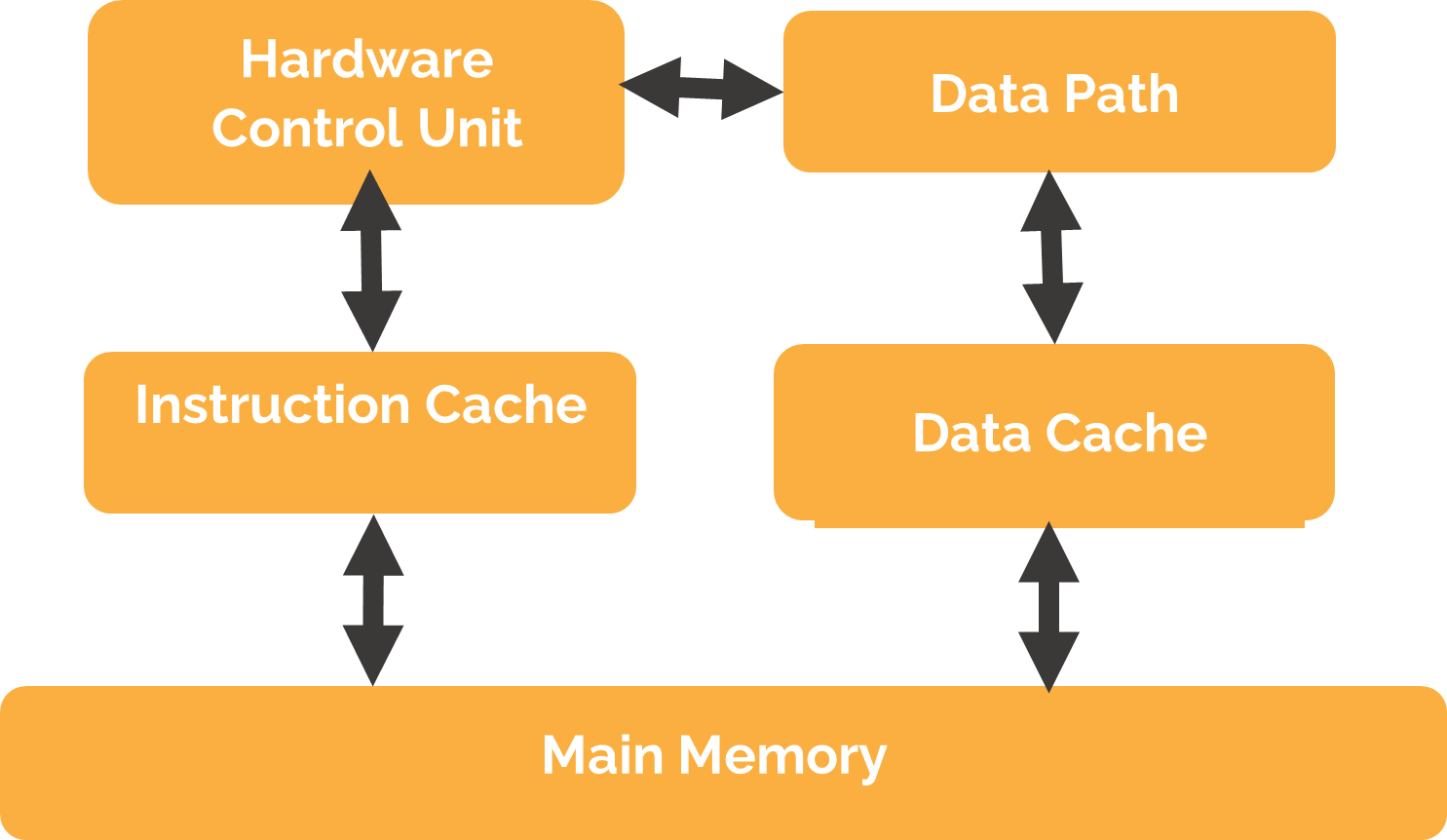

Reduced Instruction Set Computer (RISC) architecture, an alternative to CISC architecture, is described below. RISC is a microprocessor architecture with an optimized set of instructions, i.e., a single instruction can perform a single task in just one complete clock cycle, resulting in less execution time. Each clock cycle can have three parameters, i.e., fetch, decode, and execute. RISC architecture offers an optimized pipeline technique (due to the fixed length of instructions), i.e., it executes parallel instructions simultaneously.

RISC processors can have simple addressing modes, fewer data types, etc. They can support a greater number of registers (simple decoding logic), resulting in less time for memory loading/storing and a reduced instruction set (lesser number of bits used for opcode). Due to these reduced instructions, RISC architecture requires fewer transistors in hardware space while leaving more space for general-purpose registers. With all these features, the power consumption is also significantly less, and the overall performance of RISC processors is highly improved. High-level language compilers can also create efficient code due to the capabilities of a small set of instructions in RISC architecture. Accordingly, RISC architecture-based processors are commonly used in the lap, mobile phones, tablets, desktops consoles, supercomputers, and many smart devices used in automotive systems, home networking, and wireless technologies.

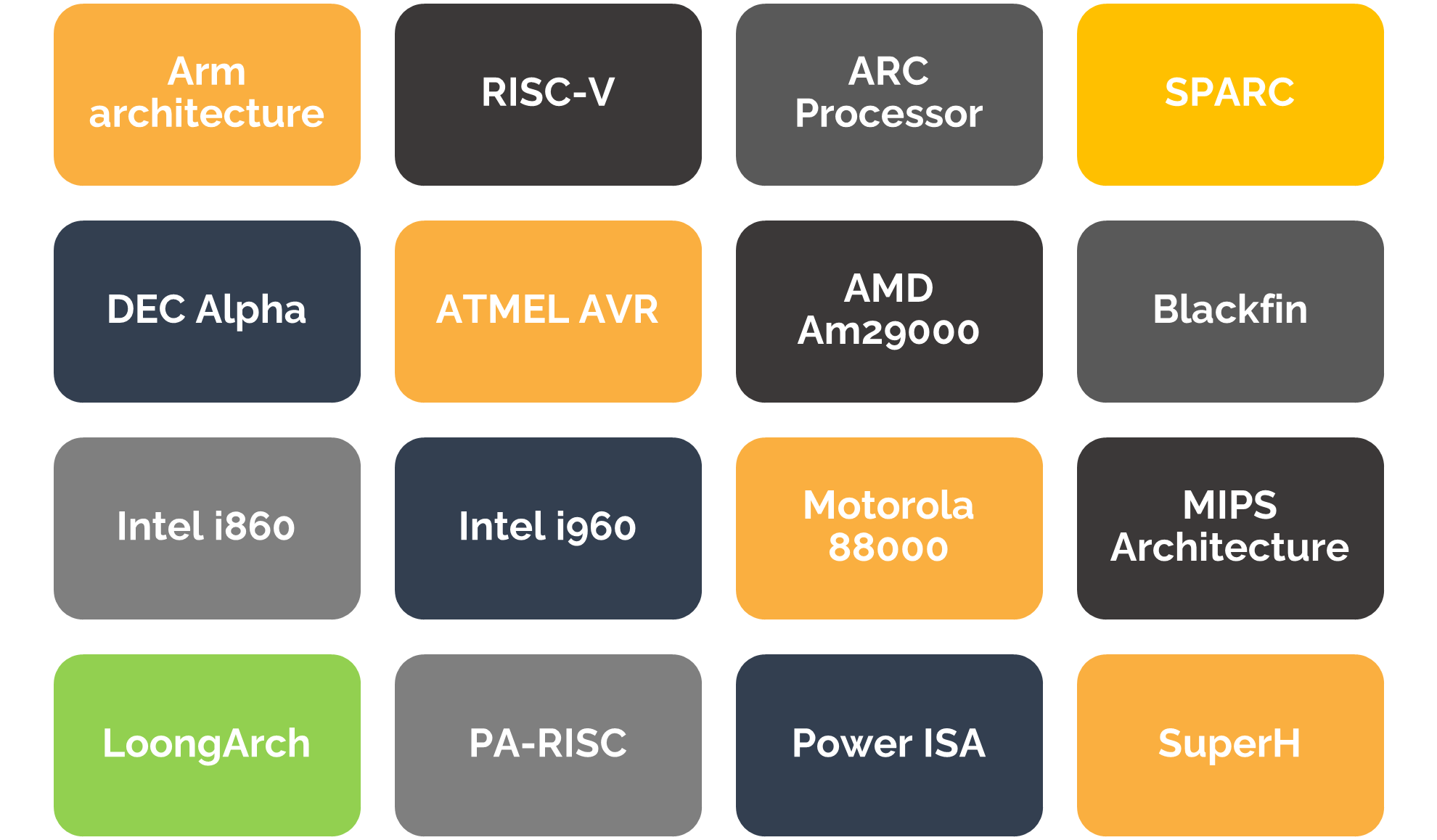

There are different types of RISC processor designs based on their architectural styles, which are listed below:

Most RISC architecture-based processors are proprietary-based, and some are based on an open-source environment. Any programmer or designer wanting to integrate proprietary-based processors into their designs must pay royalties to a particular company. But in the case of open-source RISC architecture-based processors, designers can implement their design as per standards.

Some of the RISC processor designs are described in the following sections:

ARM (Acorn RISC Machine) is a part of the RISC architecture-based family known for its processors and cores. It is proprietary-based and owned by ARM Ltd. ARM architecture supports 32-bit and 64-bit memory addresses. ARM-based on load-store architecture (i.e., load and store can occur between memory and registers) type has a set of rules and instructions which defines the interaction between hardware and software. ARM Ltd. licensed these architectures to several semiconductor companies so that they incorporate these designs into their products.

Different generations of ARM architecture designs support 32-bits and 62-bits, including ARMv1, ARMv2, ARMv3, ARMv4, ARMv5, ARMv6, ARMv7, ARMv8, ARMv8.1, ARMv8.2, ARMv8.3, ARMv8.4, ARMv8.5, ARMv8.6, ARMv8.7, ARMv9, etc. Before ARMv8, all architecture designs are based on 32-bit addressing. ARMv8 is the first ARM architecture that includes 64-bit addressing, enabling processors to combine 64-bit execution with 32-bit execution. Due to its decent performance and low power consumption, ARM chips are commonly used in smartphones, laptops, tablets, desktops, and the world’s fastest supercomputer (Fugaku).

SPARC (Scalable Processor Architecture) processors are also a part of the RISC architecture-based family developed by Sun Microsystems. SPARC is based on load-store-type architecture and supports 32-bit and 64-bit instructions. Due to its highly scalable open architecture, SPARC focuses on optimizing compilers and creating effective pipelines for hardware executions.

With all these features like high performance, scalability, and adaptability (both in terms of cost and capacity), versatility (used in commercial, technical, military, and aerospace applications), incorporated OOPS (object-oriented programming) features, and open source, SPARC is available for licensing to any individual in addition to the microprocessor manufacturers. Some SPARC processors are SPARC V7, SPARC V8, MicroSPARC, SPARC V9, UltraSPARC I, UltraSPARC II, UltraSPARC III, UltraSPARC IV, UltraSPARC T1, UltraSPARC T2, SPARC 64X, SPARC M7, SPARC M8, etc.

ARC (Argonaut RISC Core) processors are a part of the RISC architecture-based family developed by ARC International. It is based on load-store-type architecture and supports 32-bit and 64-bit instructions. ARC processors allow developers to add or remove the hardware features to optimize the cores for delivering good performance, power, and area (collectively called PPA) efficiency. ARC architecture can implement custom instructions and hardware accelerators to the cores for user-defined applications, resulting in fewer cycles and reducing energy consumption and memory requirements.

Alpha is a part of the RISC archive texture-based family with 64-bit instructions originally developed by Digital Equipment Corporation (DEC). This was implemented in microprocessors primarily used in the DEC workstations and servers.

RISC-V is an open-source ISA based on well-established RISC architecture principles, and here ‘V’ stands for 5th generation. It was developed at the University of California, Berkeley. Due to its open-source specifications, application programmers or developers can create custom instruction sets and edit or remove undesirable instructions to optimize the streamlined computation (this feature consumes less power and less area). One of the advantages of RISC-V architecture is modularity which means combining several application developers and vendor tools to create IP cores that can be used in FPGA development.

RISC-V instruction sets support 32-bit, 64-bit, and 128-bit memory addressing and extensions to support floating-point instructions. RISC-V based on load-store architecture means that ALU (arithmetic logic unit) operations can occur only between the registers and memory access (load and store) operations between memory and registers.

As we already discussed, RISC-V, with its open-source license, opens a path to several manufacturing companies in the microcontrollers and microprocessors. It also provides RISC-V hardware to the electronics market with open-source operating systems, offering high-level specificity for advanced applications like high-performance-based embedded system applications, Artificial intelligence, storage applications, edge computing, etc.

Major Players and Patenting Activities

Due to the enormous benefits of RISC architecture, it was adopted by various manufacturing companies, several other joint venture companies, research and development centers, and programmers in designing the RISC architecture-based microprocessors, microcontrollers, and other high-performance embedded system applications majorly used in communications systems, military and aerospace sectors, computing and storage, automotive sectors, healthcare and medical sectors, IoT devices, smartphones, laptops, data centers, etc.

Major Key Players

At around 15.9K patents filled over the years, IBM surpasses globally.

Last 10 Years Patent

The graph shows the trend in patent filing by these key players over the last 10 years. It can be seen that several programmers are actively involved in the research and development work in this domain.

Markets & Competitors

The graph shows the key players' involvement of different countries/regions in patent filing over the last years across the globe.

Outlook for the Next 10 Years

As the demand for semiconductor chips in the global market is increasing daily, RISC architecture has the capability which allows programmers to use this semiconductor chip more efficiently in terms of the less occupied area, power consumption, and cost-effectiveness.

The revenue generation in semiconductor chips based on RISC architecture is in billions of dollars. It will cross trillions of dollars as these chips dominate in various markets like smartphones, laptops, smart wearables, computing and storage devices, data centers, automotive sectors, healthcare and medical devices, IoT devices, military and aerospace sectors, and other electronics consumer sectors.

Last but not least, companies coordinate with various programmers, developers, and other research and development units to launch new products progressively and collaborate to increase their market shares and meet customer demands.

Author

Senior Associate at Lumenci

Mayank is a Senior Associate at Lumenci with 7+ years of experience in the semiconductor and display tech industry. Formerly a Research Associate, Mayank has hands-on experience maintaining and handling many semiconductor devices and fabrication instruments. He has co-authored several research papers in the semiconductor domain. Mayank is a Master of Technology (MTech.) Microelectronics and VLSI Design from Motilal Nehru National Institute of Technology, Allahabad, India.